Chapter 8 (Multiplexers and Demultiplexers)

Chapter 8 (Multiplexers and Demultiplexers)

Dalam dunia elektronika digital, proses penjumlahan bilangan biner merupakan operasi dasar yang penting dan sering digunakan dalam berbagai perangkat komputasi, seperti kalkulator, mikroprosesor, dan sistem kontrol digital. Salah satu rangkaian logika yang digunakan untuk operasi penjumlahan ini adalah full adder. Rangkaian full adder mampu menjumlahkan tiga buah bit input, yaitu dua bit data (A dan B) dan satu bit carry-in (Cin) dari tahapan sebelumnya, serta menghasilkan dua output berupa sum (S) dan carry-out (Co).

Biasanya, full adder dirancang menggunakan kombinasi gerbang logika dasar seperti XOR, AND, dan OR. Namun, pada eksperimen ini digunakan pendekatan berbeda, yaitu memanfaatkan decoder 3-to-8 sebagai dasar pembentukan fungsi logika output. Decoder bekerja dengan cara menghasilkan satu output aktif dari delapan output yang tersedia, berdasarkan kombinasi input biner yang diberikan. Dengan menambahkan gerbang OR pada output decoder, kita dapat membentuk fungsi logika berdasarkan minterm (penjumlahan produk) dari tabel kebenaran full adder.

Melalui metode ini, kita tidak hanya memahami cara kerja full adder, tetapi juga memperdalam konsep implementasi fungsi logika menggunakan blok fungsional seperti decoder, yang sangat berguna dalam perancangan sistem digital berskala besar.

- Tujuan dari pembelajaran ini adalah untuk: Mempelajari cara kerja full adder dan ekspresi logika keluarannya

- Mengimplementasikan full adder menggunakan komponen logika non-konvensional, yaitu decoder 3-to-8.

- Menunjukkan bahwa fungsi logika kombinasi dapat direalisasikan menggunakan decoder dan gerbang OR.

- Mengembangkan keterampilan merancang sistem digital modular.

Logic state atau keadaan logika adalah istilah dalam elektronika digital yang mengacu pada kondisi atau nilai logika dari suatu sinyal dalam sistem digital. Sistem digital bekerja berdasarkan dua level tegangan utama yang merepresentasikan dua keadaan logika, yaitu:

- Logic LOW (0)

Disebut juga logika nol atau logika rendah

Biasanya diwakili oleh tegangan rendah, contohnya:

0 Volt dalam sistem TTL (Transistor-Transistor Logic)

Tegangan antara 0–0.8V tergantung pada jenis logika

Diartikan sebagai bilangan biner 0

- Logic HIGH (1)

Disebut juga logika satu atau logika tinggi

Biasanya diwakili oleh tegangan tinggi, contohnya:

+5 Volt dalam sistem TTL

Bisa juga +3.3V atau lainnya dalam sistem CMOS modern

Diartikan sebagai bilangan biner 1

AND gate adalah salah satu gerbang logika dasar dalam sistem digital yang menghasilkan output bernilai logika tinggi (1) hanya jika semua input-nya juga bernilai tinggi (1). Jika salah satu atau semua input bernilai rendah (0), maka output-nya akan rendah (0).

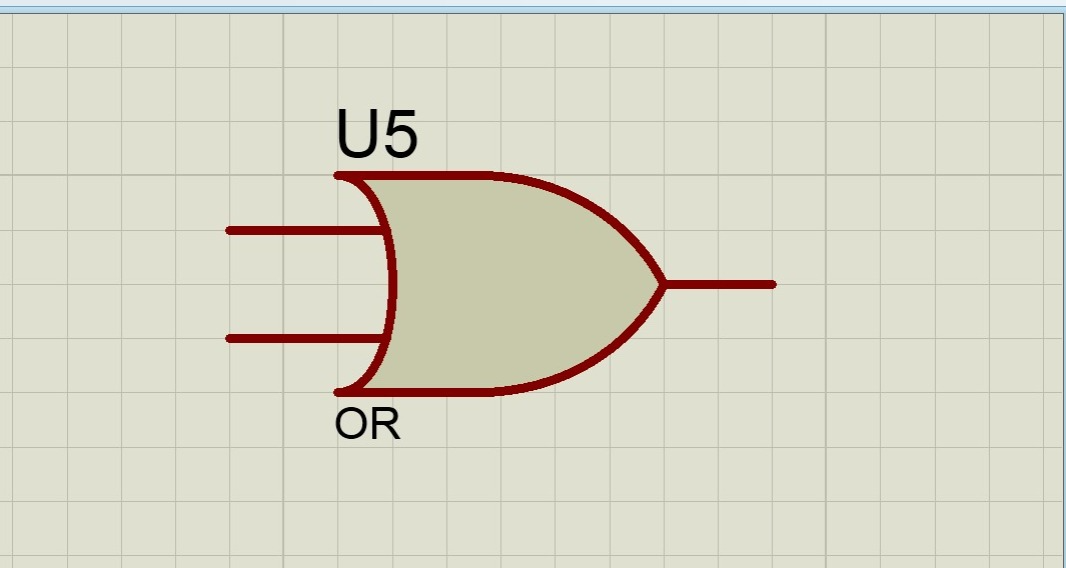

3. Or Gate

OR gate adalah salah satu gerbang logika dasar dalam sistem digital yang menghasilkan output logika tinggi (1) jika salah satu atau lebih input-nya bernilai tinggi (1). Output hanya akan rendah (0) jika semua input bernilai rendah (0).

4. Not Gate

Dalam sistem digital, decoder merupakan salah satu rangkaian logika kombinasi yang berfungsi untuk mengubah masukan biner menjadi keluaran yang bersifat eksklusif satu aktif. Decoder dengan n jalur input akan memiliki maksimal 2ⁿ jalur output. Contoh umum decoder adalah 2-to-4 decoder, 3-to-8 decoder, dan 4-to-16 decoder.

Namun, dalam penerapan nyata, seringkali jumlah jalur input dan output yang tersedia pada sebuah IC decoder tidak mencukupi kebutuhan sistem yang lebih kompleks. Untuk mengatasi keterbatasan tersebut, digunakan teknik perancangan decoder bertingkat (cascading decoder), yaitu dengan menggabungkan beberapa IC decoder kecil untuk membentuk sebuah decoder dengan kapasitas input dan output yang lebih besar.

Konsep Perancangan Decoder Bertingkat

Prinsip dasar dari perancangan decoder bertingkat adalah membagi masukan menjadi dua bagian: sebagian dihubungkan ke input decoder kecil, dan sebagian lainnya digunakan untuk mengendalikan aktivasi (enable) dari setiap decoder kecil tersebut. Dengan demikian, hanya satu decoder kecil yang aktif pada satu waktu, dan output keseluruhan sistem merupakan gabungan dari seluruh output decoder yang tersedia.

Langkah-langkah dasar dalam perancangan ini adalah sebagai berikut:

- Menentukan Jumlah Decoder yang Dibutuhkan:

Jika n adalah jumlah input dari decoder yang tersedia, dan N adalah jumlah input dari decoder yang diinginkan, maka jumlah decoder kecil yang dibutuhkan dapat dihitung dengan:

Misalnya, untuk membangun 4-to-16 decoder dari 3-to-8 decoder, dibutuhkan:

- Membagi Input Menjadi Dua Bagian

1. Bit kurang signifikan (LSB) dari input N dihubungkan langsung ke input dari setiap decoder kecil

2. Bit lebih signifikan (MSB) digunakan untuk mengaktifkan (enable) satu decoder kecil pada satu waktu.

- Mengendalikan Enable Tiap Decoder:

Decoder yang tersedia harus memiliki pin enable, sehingga hanya satu decoder yang bekerja saat kombinasi input MSB sesuai. Bit MSB ini berperan sebagai pengontrol aktivasi untuk masing-masing decoder kecil, guna mencegah dua decoder aktif secara bersamaan.

- Menggabungkan Output Decoder:

Semua output dari decoder kecil dihubungkan ke output akhir sistem, dengan urutan:

1. Output dari decoder yang diaktifkan oleh kombinasi MSB yang lebih rendah → menjadi output kurang signifikan.

2. Output dari decoder yang diaktifkan oleh kombinasi MSB yang lebih tinggi → menjadi output lebih signifikan.

Full adder merupakan rangkaian logika penting dalam sistem digital yang digunakan untuk menjumlahkan tiga bit input dan menghasilkan dua output, yaitu sum dan carry-out. Dalam implementasi tradisional, full adder dibangun dengan gerbang logika dasar. Namun, pada pendekatan ini, digunakan decoder 3-to-8 untuk membentuk fungsi logika tersebut.

Decoder digunakan untuk menghasilkan semua minterm dari kombinasi tiga input. Dengan memanfaatkan beberapa output dari decoder yang sesuai dengan minterm fungsi sum dan carry-out, serta menggabungkannya menggunakan gerbang OR, maka kita dapat menghasilkan rangkaian full adder yang fungsional. Pendekatan ini menunjukkan bahwa sistem logika digital dapat dirancang secara fleksibel dan modular, serta memberikan pemahaman mendalam tentang keterkaitan antara tabel kebenaran, minterm, dan realisasi perangkat keras digital.

A. Langkah-langkah Percobaan

Langkah-langkah Percobaan Pada Percobaan angkaian implementasi full adder menggunakan decoder 3-to-8:

Persiapan Simulasi:

Buka Proteus ISIS (atau perangkat lunak simulasi sejenis).

Buat project baru.

Penempatan Komponen:

Letakkan Decoder 3-ke-8 (misal 74LS138).

Letakkan dua Gerbang OR.

Letakkan tiga Input Logika (untuk A, B, C / Carry In).

Letakkan dua Logic Probe/LED (untuk S dan Co).

Pengkabelan Rangkaian:

Input ke Decoder: Sambungkan A, B, dan C (Carry In) dari input logika ke pin input decoder (sesuai urutan A, B, C pada decoder).

Output Sum (S): Sambungkan output decoder 1, 2, 4, 7 ke input gerbang OR pertama. Hubungkan output gerbang OR ini ke logic probe "S".

Output Carry Out (Co): Sambungkan output decoder 3, 5, 6, 7 ke input gerbang OR kedua. Hubungkan output gerbang OR ini ke logic probe "Co".

Verifikasi & Pengujian:

Jalankan simulasi.

Ubah semua 8 kombinasi input A, B, C.

Amati dan catat nilai output S dan Co untuk setiap kombinasi.

Bandingkan hasil simulasi dengan tabel kebenaran full adder standar untuk memverifikasi fungsionalitas

Prinsip Kerja Rangkaian Full Adder Menggunakan Decoder 3-ke-8 (Gambar 8.22):

Rangkaian ini bekerja dengan memanfaatkan decoder 3-ke-8 dan gerbang OR untuk melakukan penjumlahan bit.

Input: Tiga input (A, B, dan Carry In (C)) masuk ke decoder.

Fungsi Decoder: Decoder ini adalah "pemeta kombinasi". Untuk setiap kombinasi input A, B, C, decoder akan mengaktifkan satu dari delapan outputnya (D0-D7), yang masing-masing mewakili satu minterm (kombinasi input unik).

Pembentukan Sum (S):

Output decoder yang sesuai dengan minterm untuk S ('1', '2', '4', '7') dihubungkan ke sebuah gerbang OR (U12).

Gerbang OR akan menghasilkan S='1' jika salah satu minterm tersebut aktif.

Pembentukan Carry Out (Co):

Output decoder yang sesuai dengan minterm untuk Co ('3', '5', '6', '7') dihubungkan ke gerbang OR lainnya (U13).

Gerbang OR ini akan menghasilkan Co='1' jika salah satu minterm tersebut aktif.

.png)

Komentar

Posting Komentar