Chapter 7 (Arithmetic Circuits)

Chapter 7 (Arithmetic Circuits)

Dalam sistem digital, operasi penjumlahan bilangan biner menjadi salah satu proses dasar yang sangat penting karena menjadi dasar dari operasi aritmatika lainnya seperti pengurangan, perkalian, dan pembagian. Salah satu rangkaian yang digunakan untuk melakukan penjumlahan dua bilangan biner adalah four-bit binary adder, yaitu rangkaian yang terdiri dari empat full adder yang disusun secara kaskade. Meskipun disebut sebagai penjumlahan paralel, hasil dari proses penjumlahan tersebut tetap bergantung pada propagasi sinyal carry dari bit yang lebih rendah ke bit yang lebih tinggi. Hal ini menyebabkan adanya waktu tunda yang dikenal sebagai carry propagation delay, terutama ketika adder digunakan untuk bilangan dengan lebih banyak bit.

Untuk mengatasi masalah tersebut, digunakan konsep look-ahead carry generator, yaitu metode yang memungkinkan sistem untuk memprediksi nilai carry berikutnya tanpa harus menunggu hasil dari carry sebelumnya. Konsep ini menggunakan dua variabel logika, yaitu Carry Generate (G) dan Carry Propagate (P), yang secara logis dapat menghitung output carry lebih cepat dan efisien. Dengan penerapan teknik ini, semua output penjumlahan dapat diperoleh hanya dalam dua tingkat gerbang logika, sehingga mempercepat proses secara signifikan. Komponen seperti IC 74182 dapat digunakan sebagai look-ahead carry generator untuk menghasilkan input carry bagi beberapa four-bit adder sekaligus, bahkan hingga 16-bit atau lebih.

Tujuan dari praktikum ini adalah untuk:

-

Mempelajari prinsip kerja four-bit binary adder.

-

Menganalisis keterbatasan waktu propagasi carry pada rangkaian adder konvensional.

-

Menerapkan teknik look-ahead carry untuk mengurangi delay.

-

Merancang dan menguji rangkaian four-bit binary adder menggunakan look-ahead carry generato

Logic state atau keadaan logika adalah istilah dalam elektronika digital yang mengacu pada kondisi atau nilai logika dari suatu sinyal dalam sistem digital. Sistem digital bekerja berdasarkan dua level tegangan utama yang merepresentasikan dua keadaan logika, yaitu:

1. Logic LOW (0)

Disebut juga logika nol atau logika rendah

Biasanya diwakili oleh tegangan rendah, contohnya:

0 Volt dalam sistem TTL (Transistor-Transistor Logic)

Tegangan antara 0–0.8V tergantung pada jenis logika

Diartikan sebagai bilangan biner 0

2. Logic HIGH (1)

Disebut juga logika satu atau logika tinggi

Biasanya diwakili oleh tegangan tinggi, contohnya:

+5 Volt dalam sistem TTL

Bisa juga +3.3V atau lainnya dalam sistem CMOS modern

Diartikan sebagai bilangan biner 1

AND gate adalah salah satu gerbang logika dasar dalam sistem digital yang menghasilkan output bernilai logika tinggi (1) hanya jika semua input-nya juga bernilai tinggi (1). Jika salah satu atau semua input bernilai rendah (0), maka output-nya akan rendah (0).

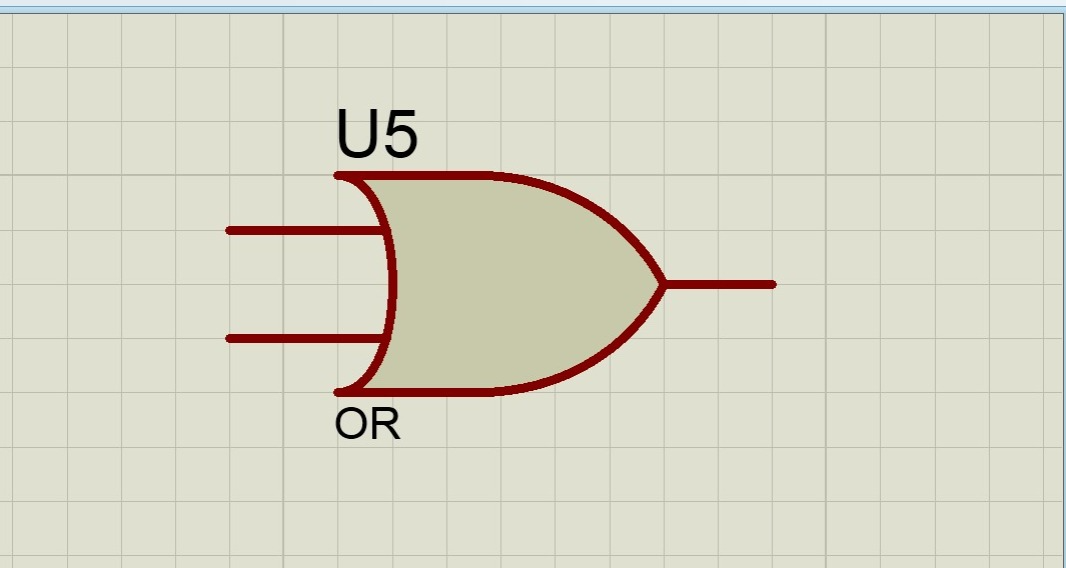

3. Or Gate

OR gate adalah salah satu gerbang logika dasar dalam sistem digital yang menghasilkan output logika tinggi (1) jika salah satu atau lebih input-nya bernilai tinggi (1). Output hanya akan rendah (0) jika semua input bernilai rendah (0).

4. XOR Gate

Logic probe adalah alat elektronik yang digunakan untuk mendeteksi dan menampilkan status logika (HIGH atau LOW) dari sinyal digital pada suatu rangkaian. Alat ini sangat berguna dalam perbaikan, pengujian, dan analisis rangkaian digital, karena memberikan informasi instan mengenai keadaan logika dari sebuah titik pengujian.

Pengantar Carry dalam Penjumlahan Biner

Dalam sistem digital, penjumlahan dua bilangan biner dilakukan dengan menggunakan full adder, yang menerima tiga input: dua bit bilangan (A dan B) dan satu carry-in dari posisi bit sebelumnya.

- Carry-in (Cin) adalah bit yang dibawa dari hasil penjumlahan sebelumnya.

- Carry-out (Cout) adalah bit yang dibawa ke posisi bit selanjutnya.

Masalah utama dalam penjumlahan biner multi-bit adalah carry propagation delay—penundaan yang terjadi saat carry harus “diteruskan” dari satu full adder ke adder berikutnya.

- Carry Propagation Delay

Ketika menggunakan penjumlah biner bertingkat seperti Ripple Carry Adder (RCA), setiap bit hasil penjumlahan harus menunggu carry dari bit sebelumnya. Hal ini menyebabkan waktu tunda total (total delay) semakin besar seiring dengan jumlah bit yang dijumlahkan.

Contoh:

Pada penjumlahan 4-bit:

- Carry-out dari bit 0 (LSB) menjadi carry-in untuk bit 1.

- Carry harus menunggu proses dari bit 0, lalu bit 1, lalu bit 2, dan seterusnya.

- Jika satu full adder memiliki delay 10 ns, maka 4-bit adder bisa mengalami delay hingga 40 ns.

Inilah yang disebut carry propagation delay, dan merupakan masalah utama dalam perancangan rangkaian aritmatika berkecepatan tinggi.

- Konsep Look-Ahead Cary

Look-Ahead Carry Generator (LACG) adalah solusi untuk mengatasi masalah carry propagation delay. Rangkaian ini menghitung seluruh carry secara paralel berdasarkan input data, tanpa menunggu hasil dari tahap sebelumnya.

LACG memanfaatkan dua sinyal logika utama:

- Generate (G):

Bit posisi tersebut akan menghasilkan carry tanpa perlu input carry.

Gi=Ai⋅Bi

- Propagate (P):

Bit posisi tersebut akan meneruskan carry jika input carry diberikan.

Dengan kedua sinyal ini, carry pada setiap posisi dapat dihitung dengan rumus logika sebagai berikut:

Dengan menghitung semua nilai carry ini secara paralel, LACG menghilangkan kebutuhan untuk menunggu hasil dari full adder sebelumnya, sehingga delay total jauh lebih kecil.

Rangkaian ini dirancang untuk mengatasi keterbatasan delay pada penjumlahan biner berantai (ripple carry) dengan cara menghitung seluruh carry secara paralel. Sistem terdiri dari dua blok utama: Full Adder 4-bit dan Look-Ahead Carry Generator (LACG).

1. Penjumlahan Awal oleh 4-Bit Binary Adder

-

Empat full adder disusun berurutan untuk menjumlahkan dua bilangan biner 4-bit:

A3A2A1A0+B3B2B1B0

-

Masing-masing full adder menerima:

-

Bit A dan B

-

Carry-in dari adder sebelumnya

-

-

Output dari setiap full adder berupa:

-

Bit hasil penjumlahan (S₀ hingga S₃)

-

Carry-out untuk adder berikutnya

-

2. Permasalahan Carry Propagation

-

Dalam ripple carry adder, carry harus menunggu hasil dari adder sebelumnya (berantai).

-

Hal ini menyebabkan carry propagation delay, yang memperlambat seluruh proses penjumlahan.

-

Delay semakin besar seiring bertambahnya jumlah bit.

3. Solusi: Look-Ahead Carry Generator (LACG)

a. Konsep Dasar

LACG menghitung seluruh nilai carry secara paralel menggunakan dua sinyal:

-

Generate (G):

-

Menghasilkan carry tanpa tergantung pada carry-in.

-

Rumus:

-

-

Propagate (P):

-

Meneruskan carry jika ada.

-

Rumus:

-

b. Persamaan Carry:

Semua carry dihitung simultan, tanpa menunggu dari full adder sebelumnya.

4. Output Akhir

-

S₀–S₃: Bit hasil penjumlahan biner.

-

C₄: Carry-out akhir (dihitung oleh LACG).

-

Dengan carry yang dihitung paralel, delay total menjadi jauh lebih kecil dibandingkan ripple carry.

Carry Propagation – Look-Ahead Carry Generator adalah rangkaian logika yang dirancang untuk mempercepat proses penjumlahan biner dengan menghitung bit carry secara paralel, tanpa menunggu hasil dari bit sebelumnya.

Pada penjumlahan biner biasa menggunakan ripple carry adder, setiap bit carry dari full adder harus menunggu hasil dari bit sebelumnya. Hal ini menimbulkan carry propagation delay, yang membuat proses penjumlahan menjadi lambat, terutama pada sistem multi-bit.

Untuk mengatasi hal ini, digunakan Look-Ahead Carry Generator (LACG) yang dapat menghitung semua nilai carry sekaligus menggunakan pendekatan logika boolean berdasarkan sinyal:

-

Generate (G): Menunjukkan bahwa posisi bit tersebut akan menghasilkan carry.

-

Propagate (P): Menunjukkan bahwa posisi bit akan meneruskan carry jika ada.

Dengan pendekatan ini, semua carry (C2, C3, C4, dst.) dihitung secara simultan, bukan berurutan, sehingga mempercepat proses penjumlahan.

A. Langkah-langkah Percobaan

Rangkaian four bit binary adder - 7.30:

- Susun rangkaian seperti Gambar 7.30 (a), sambungkan 4 full adder secara berurutan.

- Hubungkan input A (A1–A4) dan B (B1–B4) dari saklar logika.

- Beri C₀ (carry-in awal) dengan logika 0.

- Hubungkan semua output S₁–S₄ ke LED atau probe output untuk melihat hasil.

- Hubungkan carry-out akhir ke LED sebagai indikator overflow.

- Beri kombinasi input seperti:

A = 0101, B = 0011 → cek hasil: 1000

A = 1111, B = 0001 → cek hasil: 0000 dan carry = 1 - Catat semua hasil SUM (S₁–S₄) dan carry output (C₄)

- Rancang rangkaian seperti Gambar 7.31, bangun LACG menggunakan gerbang logika.

- Masukkan nilai A dan B dari saklar (P dan G dihitung dari A dan B).

Gᵢ = Aᵢ · Bᵢ

Pᵢ = Aᵢ + Bᵢ - Inputkan nilai carry-in awal C₁ = 0 atau 1.

- Amati output carry C₂, C₃, dan C₄ pada LED sesuai fungsi:

C i + 1 = G i + P i ⋅ C i C_{i+1} = G_i + P_i \cdot C_i - Coba beberapa kombinasi input, misalnya:

A = 0101, B = 0011, C₁ = 0

A = 1111, B = 1111, C₁ = 1 - Bandingkan kecepatan atau hasilnya dengan full adder biasa.

Rangkaian ini terdiri dari empat Full Adder (FA) yang disusun secara berantai untuk menjumlahkan dua bilangan biner 4-bit, yaitu input A (A1–A4) dan input B (B1–B4). Setiap FA menjumlahkan pasangan bit A dan B bersama carry-in, menghasilkan bit penjumlahan (S) dan carry-out.

-

Carry-out dari FA pertama menjadi carry-in untuk FA kedua, dan seterusnya.

-

Proses penjumlahan dimulai dari bit LSB (A1, B1) hingga MSB (A4, B4).

-

Rangkaian bekerja berdasarkan prinsip ripple carry, di mana carry menyebar dari kiri ke kanan.

Contoh:

-

Input A = 1001 (A4–A1), B = 0111 (B4–B1), Carry-in awal = 0

-

Penjumlahan: 1001 + 0111 = 10000 (hasil 5-bit)

-

Output S = 0000 (S4–S1), Carry-out = 1

Look-Ahead Carry Generator (LACG) adalah rangkaian logika yang digunakan untuk mempercepat proses perhitungan carry pada sistem penjumlahan biner, seperti pada 4-bit binary adder. Berbeda dengan metode ripple carry yang menghitung carry secara berantai (satu per satu), LACG menghitung semua carry secara paralel menggunakan sinyal Generate (G) dan Propagate (P).

Dengan teknik ini, delay (waktu tunggu) akibat penyebaran carry antar bit dapat dikurangi secara signifikan, sehingga sangat berguna dalam sistem digital berkecepatan tinggi seperti ALU dan prosesor.

Look-Ahead Carry Generator (LACG) berfungsi mempercepat proses perhitungan carry dengan menghitung semua carry secara paralel, menggunakan sinyal Propagate (P) dan Generate (G).

-

Generate (G): Menghasilkan carry tanpa bantuan carry-in.

-

Propagate (P): Meneruskan carry jika ada carry-in.

Carry-out dihitung dengan logika:

-

C2 = G1 + (P1 · C1)

-

C3 = G2 + (P2 · G1) + (P2 · P1 · C1)

-

C4 = G3 + (P3 · G2) + (P3 · P2 · G1) + (P3 · P2 · P1 · C1)

Contoh:

-

Input P = 1,0,1 (P1–P3), G = 0,1,0 (G1–G3), C1 = 0

-

Hasil: C2 = 0, C3 = 1, C4 = 1

.png)

Komentar

Posting Komentar