Chapter 11.17 (MOD-4 counter with decoding gates)

Chapter 11 (MOD-4 counter with decoding gates)

Pencacah (counter) adalah fondasi penting dalam rancangan sistem digital, berperan vital dalam penjadwalan, pembagian frekuensi, dan pengaturan logika. Ada dua jenis utama: ripple counter (asinkron) dan synchronous counter. Meskipun ripple counter menonjol karena desainnya yang sederhana dan hemat gerbang, operasi asinkronnya—di mana setiap flip-flop dipicu oleh output sebelumnya—sering menimbulkan kesulitan, terutama ketika output pencacah perlu diuraikan atau didekode.

Permasalahan utama pada ripple counter adalah timbulnya glitches (pulsa singkat tak diinginkan) pada output gerbang dekode. Ini terjadi karena adanya tunda rambat (propagation delay) yang terakumulasi dari satu flip-flop ke berikutnya. Saat clock bertransisi, flip-flop tidak berganti keadaan secara bersamaan; setiap flip-flop butuh waktu respons, menciptakan periode singkat di mana kombinasi output flip-flop belum stabil. Ketidakstabilan temporer ini dapat memicu glitches pada gerbang dekode, seperti yang terbukti pada pencacah MOD-4. Karena glitches dapat memicu malfungsi dalam sistem sensitif, penanganannya menjadi krusial. Salah satu pendekatan efektif adalah penggunaan sinyal strobe, yang menonaktifkan gerbang dekode sementara hingga semua flip-flop berada dalam kondisi stabil.

tujuan percobaan glitches pada ripple counter:

- Mengamati dan Menganalisis Glitches

- Mengidentifikasi Kondisi Penyebab Glitches

- Menerapkan Solusi Sinyal Strobe

- Membandingkan Kualitas Sinyal Dekode

Logic state atau keadaan logika adalah istilah dalam elektronika digital yang mengacu pada kondisi atau nilai logika dari suatu sinyal dalam sistem digital. Sistem digital bekerja berdasarkan dua level tegangan utama yang merepresentasikan dua keadaan logika, yaitu:

1. Logic LOW (0)

Disebut juga logika nol atau logika rendah

Biasanya diwakili oleh tegangan rendah, contohnya:

0 Volt dalam sistem TTL (Transistor-Transistor Logic)

Tegangan antara 0–0.8V tergantung pada jenis logika

Diartikan sebagai bilangan biner 0

2. Logic HIGH (1)

Disebut juga logika satu atau logika tinggi

Biasanya diwakili oleh tegangan tinggi, contohnya:

+5 Volt dalam sistem TTL

Bisa juga +3.3V atau lainnya dalam sistem CMOS modern

Diartikan sebagai bilangan biner 1

AND gate adalah salah satu gerbang logika dasar dalam sistem digital yang menghasilkan output bernilai logika tinggi (1) hanya jika semua input-nya juga bernilai tinggi (1). Jika salah satu atau semua input bernilai rendah (0), maka output-nya akan rendah (0).

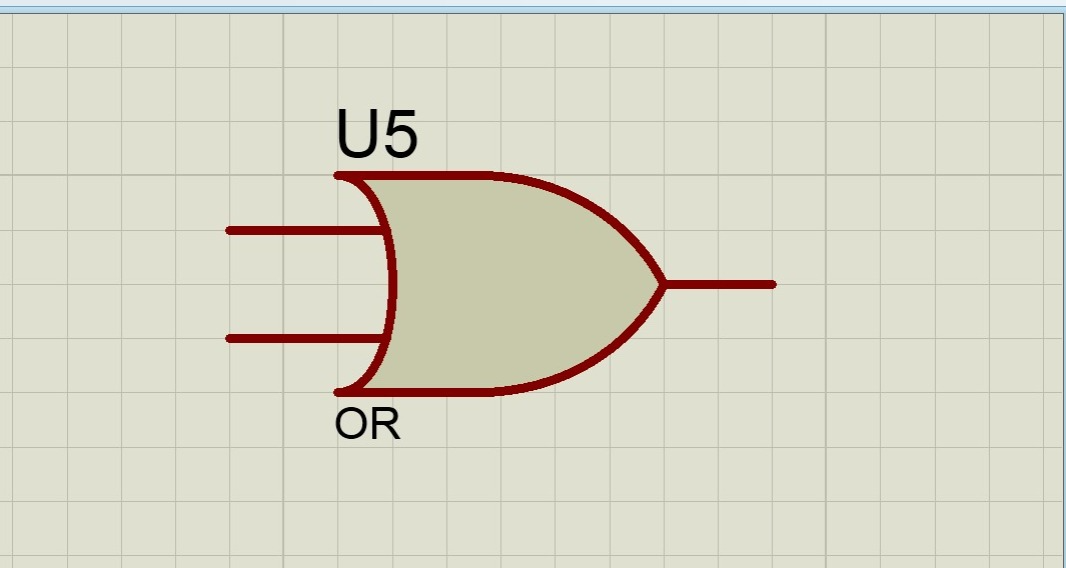

3. Or Gate

OR gate adalah salah satu gerbang logika dasar dalam sistem digital yang menghasilkan output logika tinggi (1) jika salah satu atau lebih input-nya bernilai tinggi (1). Output hanya akan rendah (0) jika semua input bernilai rendah (0).

4. Not Gate

Logic probe adalah alat elektronik yang digunakan untuk mendeteksi dan menampilkan status logika (HIGH atau LOW) dari sinyal digital pada suatu rangkaian. Alat ini sangat berguna dalam perbaikan, pengujian, dan analisis rangkaian digital, karena memberikan informasi instan mengenai keadaan logika dari sebuah titik pengujian.

1. Konsep Dasar dan Klasifikasi Pencacah (Counter)

Pencacah (counter) merupakan salah satu blok fungsional esensial dalam sistem elektronika digital, yang berperan dalam menghitung jumlah pulsa clock yang diterima. Fungsi utamanya sangat vital dalam berbagai aplikasi, seperti pembagian frekuensi, pengalamatan memori, dan implementasi kontrol sekuensial. Berdasarkan metode pemicuan flip-flop oleh sinyal clock, pencacah dapat dikelompokkan menjadi dua kategori utama:

- Pencacah Asinkron (Ripple Counter): Pada jenis ini, flip-flop tersusun secara berantai, di mana output dari satu flip-flop berfungsi sebagai sinyal clock untuk flip-flop berikutnya. Akibatnya, perubahan keadaan flip-flop tidak terjadi secara simultan, melainkan merambat (ripple) dari satu tahap ke tahap berikutnya.

- Pencacah Sinkron (Synchronous Counter): Berbeda dengan pencacah asinkron, semua flip-flop dalam pencacah sinkron dipicu secara bersamaan oleh satu sinyal clock yang sama, memastikan transisi keadaan yang serempak.

2. Pencacah Modulus-N (MOD-N)

Istilah Modulus N (MOD-N) merujuk pada jumlah keadaan diskrit dan unik yang dapat dihitung oleh sebuah pencacah sebelum siklus hitungannya berulang ke keadaan awal. Sebagai ilustrasi, sebuah pencacah MOD-4 akan melalui empat keadaan berbeda (misalnya, 00, 01, 10, 11) sebelum kembali ke 00. Secara umum, untuk mencapai N keadaan, sebuah pencacah memerlukan setidaknya buah flip-flop. Dengan demikian, pencacah MOD-4 dapat diimplementasikan menggunakan dua buah flip-flop (karena ).

3. Fungsi Gerbang Dekode

Output dari sebuah pencacah, yang disajikan dalam bentuk kombinasi biner dari keadaan flip-flop (contohnya, Q1Q0), seringkali perlu diinterpretasikan atau "didekode" menjadi sinyal diskrit yang merepresentasikan setiap keadaan uniknya. Proses dekode ini direalisasikan menggunakan gerbang dekode. Gerbang dekode adalah konfigurasi gerbang logika (umumnya gerbang AND atau NAND) yang didesain untuk menghasilkan output aktif (HIGH atau LOW, tergantung spesifikasi) hanya ketika inputnya (yaitu, kombinasi output Q dan dari flip-flop) sesuai dengan representasi biner dari suatu keadaan spesifik. Contohnya, untuk mendekode keadaan '00' pada pencacah MOD-4, sebuah gerbang AND akan memerlukan input dari dan .

4. Permasalahan Glitches pada Gerbang Dekode Ripple Counter

Meskipun ripple counter unggul dalam kesederhanaan, karakteristik asinkronnya menimbulkan isu krusial ketika outputnya dihubungkan ke gerbang dekode: kemunculan glitches atau spikes (pulsa singkat yang tidak dikehendaki) pada waveform output gerbang dekode. Fenomena ini diakibatkan oleh beberapa faktor:

- Penundaan Propagasi Kumulatif: Setiap flip-flop memiliki propagation delay (tPLH/tPHL), yaitu waktu yang dibutuhkan output untuk berubah setelah transisi clock. Pada ripple counter, penundaan ini bersifat akumulatif seiring dengan perambatan sinyal antar flip-flop. Misalnya, dalam transisi keadaan dari '01' ke '10', flip-flop pertama (Q0) akan berubah dari 1 ke 0, dan flip-flop kedua (Q1) baru akan merespons transisi Q0 setelah adanya penundaan.

- Keadaan Transien yang Tidak Stabil: Selama periode penundaan propagasi ini, terdapat momen-momen singkat di mana kombinasi output flip-flop (misalnya Q1Q0) berada dalam keadaan transien atau tidak stabil. Keadaan ini bukan merupakan bagian dari urutan hitungan yang valid. Sebagai ilustrasi, saat bertransisi dari '01' menuju '10', kombinasi output dapat secara temporer melewati '00' atau '11' sebelum akhirnya mencapai '10' yang stabil.

- Pemicuan Gerbang Dekode yang Keliru: Gerbang dekode, yang dirancang untuk merespons kombinasi input tertentu (misalnya, untuk mendeteksi '00'), dapat secara keliru terpicu oleh keadaan transien yang tidak stabil ini. Hal ini menghasilkan pulsa glitch yang singkat namun berpotensi memicu operasi yang tidak diinginkan atau kesalahan logika pada sirkuit berikutnya.

5. Solusi Mitigasi Glitches: Pemanfaatan Sinyal Strobe

Untuk mengatasi masalah glitches ini, salah satu metode yang efektif adalah implementasi sinyal strobe. Sinyal strobe adalah pulsa kontrol eksternal yang berfungsi untuk menonaktifkan (disable) gerbang dekode secara sementara. Gerbang dekode akan tetap dinonaktifkan hingga semua flip-flop dalam ripple counter telah menyelesaikan transisi ke keadaan stabil sebagai respons terhadap transisi clock yang relevan. Dengan demikian, gerbang dekode hanya diizinkan untuk memproses dan menghasilkan sinyal dekode yang valid setelah semua glitches transien telah mereda. Sinyal strobe ini umumnya dihasilkan dengan penundaan waktu yang terukur dari pulsa clock utama, memastikan bahwa semua flip-flop memiliki waktu yang memadai untuk mencapai kondisi stabil sebelum output dekode dibaca.

Pencacah (counter) adalah komponen esensial dalam sistem digital, yang terbagi menjadi ripple counter (asinkron) dan synchronous counter. Meskipun ripple counter sederhana dalam desainnya, sifat operasinya yang asinkron—di mana setiap flip-flop dipicu secara berurutan—menimbulkan masalah serius, terutama saat outputnya perlu didekode. Permasalahan utama adalah kemunculan glitches atau pulsa tak diinginkan pada output gerbang dekode. Glitches ini diakibatkan oleh penundaan propagasi kumulatif antar flip-flop, yang menciptakan keadaan transien tidak stabil pada kombinasi output pencacah. Gerbang dekode kemudian secara keliru merespons keadaan transien ini, menghasilkan pulsa glitch yang singkat namun berpotensi menyebabkan kesalahan fungsional dalam sistem.

Untuk mengatasi glitches yang merugikan ini, terutama yang sangat menonjol pada ripple counter seperti pencacah MOD-4, salah satu solusi efektif adalah penggunaan sinyal strobe. Sinyal strobe berfungsi sebagai pengontrol yang menonaktifkan gerbang dekode untuk sementara waktu, memastikan bahwa gerbang tersebut hanya aktif setelah semua flip-flop dalam pencacah telah mencapai keadaan stabil dan valid pasca transisi clock. Dengan demikian, sinyal strobe memungkinkan pembacaan output dekode yang bersih dan bebas glitch, menjaga integritas dan keandalan operasi sistem digital.

A. Langkah-langkah Percobaan

- Persiapan Software:Pastikan Anda sudah menginstal software Proteus di komputer

- Membuat Rangkaian - Jalankan aplikasi Proteus.- Pilih "New Project" dan beri nama proyek Anda- Cari dan tambahkan komponen berikut:

- JK Flip-Flop (74LS76) sebanyak 2 buah.

- Clock Pulse (Generator Gelombang) untuk memberikan sinyal clock.

- Decoder (misalnya 2-to-4 Decoder) sesuai kebutuhan.

- Hubungkan output dari flip-flop pertama ke input dari flip-flop kedua.

- Hubungkan sinyal clock ke input CLK pada flip-flop.

- Pastikan semua pin dihubungkan dengan benar

- Konfigurasi Flip-Flop:

Setel pin J dan K pada flip-flop sesuai logika yang diinginkan untuk operasi MOD-4 (biasanya J dan K dihubungkan ke HIGH). - Menambahkan Sumber Daya:

Tambahkan sumber daya untuk memastikan setiap komponen mendapatkan tegangan yang sesuai. - Simulasi Rangkaian:

- Setelah semua komponen terhubung, klik tombol "Play" untuk memulai simulasi.

- Observasi output dari flip-flop dan bagaimana dekoder menampilkan hasil.

.png)

Komentar

Posting Komentar