Chapter 11.45 (Four-bit ring counter)

Chapter 11.45 (Four-bit ring counter)

Dalam elektronika digital, flip-flop merupakan blok pembangun dasar yang dapat diatur dalam berbagai konfigurasi untuk membentuk rangkaian sekuensial yang kompleks. Salah satu konfigurasi umum adalah shift register, yaitu susunan flip-flop yang memungkinkan pergeseran data secara serial. Namun, shift register pada dasarnya tidak memiliki urutan keadaan yang ditentukan. Ketika output serial dari sebuah shift register diumpan balikkan ke input serialnya, rangkaian yang dihasilkan akan menunjukkan urutan keadaan yang spesifik dan terulang. Rangkaian jenis ini dikenal sebagai shift register counter.

Ring counter adalah salah satu jenis shift register counter yang diperoleh dengan mengumpan balikkan secara langsung output sebenarnya dari flip-flop terakhir ke input data dari flip-flop input pertama. Rangkaian ini, yang juga disebut circulating register, menghasilkan siklus keadaan yang terdefinisi dengan jelas setiap kali menerima pulsa clock. Percobaan ini akan mengeksplorasi prinsip kerja dan karakteristik dari four-bit ring counter, seperti yang digambarkan dalam Figure 11.45, serta mengamati urutan keadaan yang dihasilkannya.

Tujuan Percobaan

Memahami prinsip dasar dan struktur rangkaian dari sebuah four-bit ring counter.

Mengamati dan memverifikasi urutan keadaan spesifik yang dihasilkan oleh ring counter per setiap pulsa clock.

Menganalisis peran umpan balik dari output flip-flop terakhir ke input flip-flop pertama dalam membentuk siklus hitungan.

Melihat utilitas ring counter sebagai elemen kontrol untuk menghasilkan pulsa kontrol yang terjadi secara berurutan.

Logic state atau keadaan logika adalah istilah dalam elektronika digital yang mengacu pada kondisi atau nilai logika dari suatu sinyal dalam sistem digital. Sistem digital bekerja berdasarkan dua level tegangan utama yang merepresentasikan dua keadaan logika, yaitu:

1. Logic LOW (0)

Disebut juga logika nol atau logika rendah

Biasanya diwakili oleh tegangan rendah, contohnya:

0 Volt dalam sistem TTL (Transistor-Transistor Logic)

Tegangan antara 0–0.8V tergantung pada jenis logika

Diartikan sebagai bilangan biner 0

2. Logic HIGH (1)

Disebut juga logika satu atau logika tinggi

Biasanya diwakili oleh tegangan tinggi, contohnya:

+5 Volt dalam sistem TTL

Bisa juga +3.3V atau lainnya dalam sistem CMOS modern

Diartikan sebagai bilangan biner 1

AND gate adalah salah satu gerbang logika dasar dalam sistem digital yang menghasilkan output bernilai logika tinggi (1) hanya jika semua input-nya juga bernilai tinggi (1). Jika salah satu atau semua input bernilai rendah (0), maka output-nya akan rendah (0).

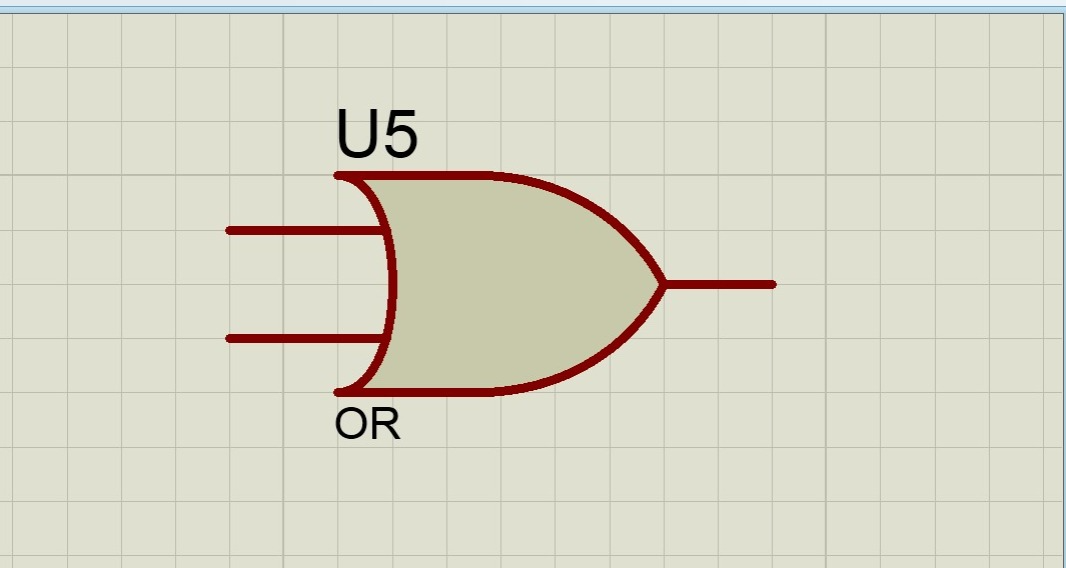

3. Or Gate

OR gate adalah salah satu gerbang logika dasar dalam sistem digital yang menghasilkan output logika tinggi (1) jika salah satu atau lebih input-nya bernilai tinggi (1). Output hanya akan rendah (0) jika semua input bernilai rendah (0).

4. Not Gate

Logic probe adalah alat elektronik yang digunakan untuk mendeteksi dan menampilkan status logika (HIGH atau LOW) dari sinyal digital pada suatu rangkaian. Alat ini sangat berguna dalam perbaikan, pengujian, dan analisis rangkaian digital, karena memberikan informasi instan mengenai keadaan logika dari sebuah titik pengujian.

1. Pencacah Shift Register (Shift Register Counters)

Pencacah shift register adalah rangkaian sekuensial yang dibentuk dari flip-flop yang terhubung dalam konfigurasi shift register dan dilengkapi dengan jalur umpan balik dari output ke inputnya. Berbeda dengan pencacah biner konvensional yang mengikuti urutan hitung biner standar, shift register counter menghasilkan serangkaian keadaan yang telah ditentukan sebelumnya karena adanya umpan balik. Dua jenis utama dari shift register counter adalah ring counter dan shift counter (atau Johnson counter).

2. Ring Counter

Ring counter merupakan jenis shift register counter yang paling sederhana dan sering juga disebut sebagai circulating register. Konsep dasarnya melibatkan pengumpanan balik langsung output sebenarnya (Q) dari flip-flop terakhir ke terminal input data (D atau J-K) dari flip-flop pertama.

Konstruksi dengan D Flip-Flop:

Apabila flip-flop tipe D digunakan (seperti 74LS74 yang terilustrasi dalam Figure 11.45), output Q dari flip-flop terakhir (contohnya U2:B pada Figure 11.45) dihubungkan kembali ke input D dari flip-flop pertama (U1:A pada Figure 11.45). Seluruh flip-flop dalam rangkaian ini dipicu secara serentak oleh sinyal clock yang sama.

Konstruksi dengan J-K Flip-Flop:

Jika flip-flop tipe J-K digunakan, output Q dan dari flip-flop terakhir masing-masing diumpan balikkan ke input J dan K dari flip-flop pertama.

Urutan Keadaan (Four-bit Ring Counter):

Sebuah four-bit ring counter (sebagaimana terlihat dalam Figure 11.45) memiliki urutan keadaan yang sangat spesifik. Jika flip-flop pertama (FF0/U1:A) diawali dengan logika '1' dan flip-flop lainnya direset ke '0' (menghasilkan keadaan awal 1000):

Dengan pulsa clock pertama, logika '1' akan bergeser ke output flip-flop kedua, sehingga output pencacah menjadi 0100.

Pulsa clock kedua mengubah output menjadi 0010.

Pulsa clock ketiga mengubah output menjadi 0001.

Dengan pulsa clock keempat, logika '1' yang kini berada di flip-flop terakhir akan diumpan balikkan ke flip-flop pertama, mengembalikan output pencacah ke 1000. Siklus ini akan terus berulang pada pulsa clock berikutnya. Sebuah ring counter N-bit yang diinisialisasi dengan satu '1' akan menghasilkan N keadaan unik dalam satu siklus penuh.

3. Aplikasi Ring Counter

Circulating register atau ring counter seringkali ditemukan dalam bagian kontrol sistem berbasis mikroprosesor dan aplikasi digital lainnya. Mereka berfungsi sebagai elemen timing dan kontrol yang sangat efektif untuk menghasilkan serangkaian pulsa kontrol yang harus terjadi satu per satu secara berurutan, memastikan eksekusi peristiwa yang tepat dan terurut secara sekuensial.

A. Langkah-langkah Percobaan

A. Siapkan Komponen di Proteus:

Cari dan tempatkan IC:

74LS74(2 buah).Tambahkan sumber clock:

CLOCK.Tambahkan indikator:

LED-RED(4 buah) danRES(Resistor, 4 buah).Tambahkan input kontrol:

LOGICSTATE(4 buah, untuk inisialisasi PR/CLR).Tambahkan instrumen:

OSCILLOSCOPE.

B. Buat Rangkaian (Lihat Gambar 11.45 sebagai panduan):

Hubungkan Daya: Sambungkan VCC dan GND ke semua IC.

Clock Bersama: Sambungkan output

CLOCKke pin clock semua flip-flop (pin 3 dan 11 pada setiap 74LS74).Rantai Geser: Sambungkan output Q dari satu flip-flop ke input D flip-flop berikutnya (Q dari U1:A ke D U1:B, Q U1:B ke D U2:A, Q U2:A ke D U2:B).

Loop Umpan Balik: Sambungkan output Q dari flip-flop terakhir (Q dari U2:B) kembali ke input D flip-flop pertama (D dari U1:A).

Inisialisasi (PR/CLR):

Untuk Q0='1': Sambungkan pin PR (Preset) U1:A ke

LOGICSTATEdan pin CLR kePOWER.Untuk Q1='0', Q2='0', Q3='0': Sambungkan pin CLR dari U1:B, U2:A, U2:B ke

LOGICSTATEdan pin PR kePOWER.

Indikator: Pasang 4 LED (dengan resistor) di output Q dari setiap flip-flop.

C. Lakukan Pengujian (Simulasi):

Set Keadaan Awal (1000):

Jalankan simulasi (tombol "Play").

Ubah

LOGICSTATEyang terhubung ke PR U1:A menjadi LOW sesaat, lalu kembalikan HIGH.Ubah

LOGICSTATEyang terhubung ke CLR U1:B, U2:A, U2:B menjadi LOW sesaat, lalu kembalikan HIGH. Ini akan mengatur LED ke 1000.

Amati Hitungan:

Atur frekuensi

CLOCKmenjadi 1 Hz (klik dua kaliCLOCK).Perhatikan LED. Anda akan melihat '1' bergeser dari satu LED ke LED berikutnya (1000 0100 0010 0001), lalu kembali ke 1000.

Lihat Bentuk Gelombang:

Hentikan simulasi. Ubah frekuensi

CLOCKmenjadi 1 kHz.Seret

OSCILLOSCOPEke rangkaian.Sambungkan setiap probe osiloskop (A, B, C, D) ke output Q dari masing-masing flip-flop.

Jalankan simulasi. Anda akan melihat empat gelombang yang sama, tetapi bergeser waktunya, menunjukkan pergeseran '1'.

Prinsip Kerja Rangkaian Four-bit Ring Counter

Rangkaian 11.45 menggambarkan sebuah four-bit ring counter yang dibangun menggunakan empat buah D flip-flop (dalam hal ini, dua IC 74LS74, di mana setiap IC memiliki dua D flip-flop). Ring counter adalah jenis khusus dari shift register counter yang menghasilkan urutan keadaan yang telah ditentukan melalui umpan balik.

Bagaimana Ia Bekerja:

Struktur Dasar: Rangkaian ini adalah shift register 4-bit, di mana output Q dari setiap flip-flop dihubungkan ke input D dari flip-flop berikutnya secara serial. Semua flip-flop menerima pulsa clock yang sama secara sinkron.

Umpan Balik: Fitur kunci dari ring counter adalah umpan balik langsung dari output Q dari flip-flop terakhir (FF3 atau U2:B) ke input D dari flip-flop pertama (FF0 atau U1:A). Inilah yang membentuk "cincin" atau "sirkulasi" data.

Inisialisasi Penting: Agar ring counter berfungsi dengan benar dan menghasilkan siklus yang diinginkan, ia harus diinisialisasi ke keadaan awal yang spesifik. Misalnya, jika diinisialisasi ke 1000 (FF0=1, FF1=0, FF2=0, FF3=0), sebuah logika '1' tunggal dimasukkan ke dalam rangkaian, sementara flip-flop lainnya berlogika '0'. Tanpa inisialisasi yang tepat, counter bisa macet di keadaan 0000 atau pola acak lainnya.

Proses Pergeseran:

Setiap kali pulsa clock positif (atau tepi clock yang aktif, tergantung jenis flip-flop) tiba, data dari output Q setiap flip-flop akan bergeser ke flip-flop berikutnya.

Logika '1' yang awalnya ada di FF0 akan bergeser ke FF1 pada pulsa clock pertama, lalu ke FF2 pada pulsa clock kedua, dan seterusnya, hingga mencapai FF3.

Ketika logika '1' mencapai FF3, pada pulsa clock berikutnya, ia akan diumpan balikkan kembali ke FF0 melalui koneksi umpan balik.

Urutan Keadaan: Proses ini menciptakan siklus berulang dari keadaan: 1000 0100 0010 0001 1000, dan seterusnya. Untuk N flip-flop (N-bit ring counter), akan ada N keadaan unik dalam satu siklus penuh, asalkan diinisialisasi dengan satu '1'.

Aplikasi: Ring counter sangat berguna sebagai elemen kontrol dalam sistem digital, khususnya dalam sistem berbasis mikroprosesor, untuk menghasilkan urutan pulsa kontrol yang harus terjadi satu per satu secara sekuensial.

.png)

Komentar

Posting Komentar