11.47 (Four-bit shift counter)

Chapter 11.47 (Four-bit shift counter)

Dalam ranah elektronika digital, shift register merupakan konfigurasi dasar flip-flop yang memungkinkan pergeseran data secara berurutan. Meskipun shift register pada dasarnya tidak memiliki pola keadaan yang tetap, pengenalan jalur umpan balik dari outputnya kembali ke input dapat mengubahnya menjadi shift register counter, yang menghasilkan urutan kondisi yang telah ditentukan.

Secara spesifik, shift counter — dikenal juga sebagai Johnson counter — adalah variasi shift register counter yang khas, dibedakan oleh penggunaan umpan balik yang terbalik (inverse feedback). Berlawanan dengan ring counter yang menggunakan umpan balik langsung, shift counter mengarahkan output invers dari flip-flop terakhir ke input flip-flop pertama. Susunan ini memungkinkan shift counter menghasilkan deretan keadaan yang lebih panjang dan unik dibandingkan dengan ring counter dengan jumlah flip-flop yang setara. Studi ini akan menelusuri bagaimana four-bit shift counter beroperasi dan urutan kondisi yang dihasilkannya, seperti yang diilustrasikan dalam Figure 11.47.

Tujuan Percobaan

Memahami prinsip operasional dan susunan internal dari sebuah four-bit shift counter (Johnson counter).

Mengamati dan memverifikasi deretan kondisi unik yang tercipta oleh shift counter setelah setiap pulsa clock.

Menganalisis mekanisme umpan balik terbalik, fitur pembeda utama dari shift counter.

Melihat dan membandingkan timing waveform yang dihasilkan oleh shift counter dengan pola keadaan yang telah ditetapkan secara teoritis.

Logic state atau keadaan logika adalah istilah dalam elektronika digital yang mengacu pada kondisi atau nilai logika dari suatu sinyal dalam sistem digital. Sistem digital bekerja berdasarkan dua level tegangan utama yang merepresentasikan dua keadaan logika, yaitu:

1. Logic LOW (0)

Disebut juga logika nol atau logika rendah

Biasanya diwakili oleh tegangan rendah, contohnya:

0 Volt dalam sistem TTL (Transistor-Transistor Logic)

Tegangan antara 0–0.8V tergantung pada jenis logika

Diartikan sebagai bilangan biner 0

2. Logic HIGH (1)

Disebut juga logika satu atau logika tinggi

Biasanya diwakili oleh tegangan tinggi, contohnya:

+5 Volt dalam sistem TTL

Bisa juga +3.3V atau lainnya dalam sistem CMOS modern

Diartikan sebagai bilangan biner 1

AND gate adalah salah satu gerbang logika dasar dalam sistem digital yang menghasilkan output bernilai logika tinggi (1) hanya jika semua input-nya juga bernilai tinggi (1). Jika salah satu atau semua input bernilai rendah (0), maka output-nya akan rendah (0).

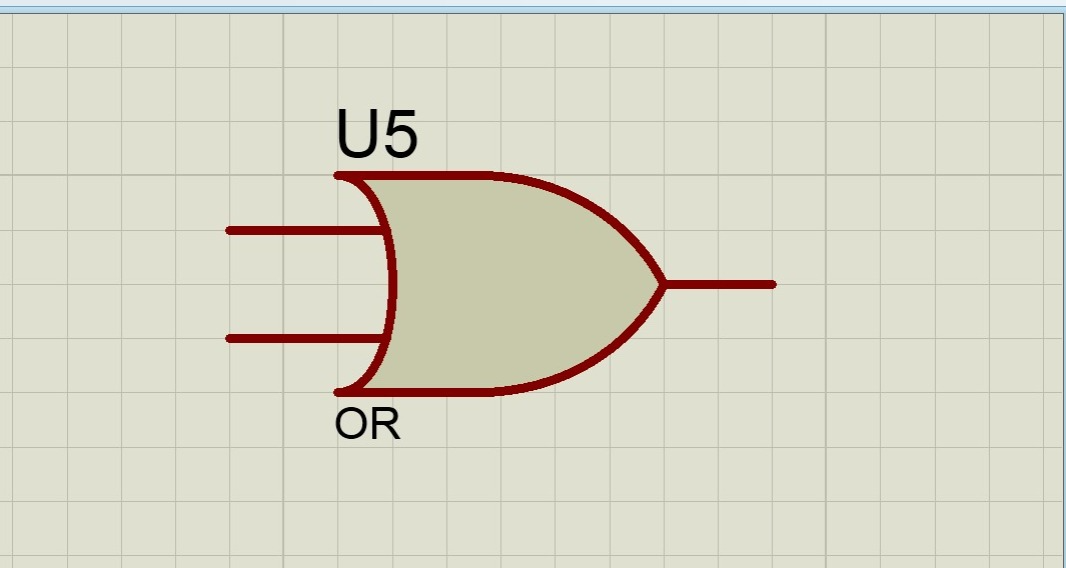

3. Or Gate

OR gate adalah salah satu gerbang logika dasar dalam sistem digital yang menghasilkan output logika tinggi (1) jika salah satu atau lebih input-nya bernilai tinggi (1). Output hanya akan rendah (0) jika semua input bernilai rendah (0).

4. Not Gate

Logic probe adalah alat elektronik yang digunakan untuk mendeteksi dan menampilkan status logika (HIGH atau LOW) dari sinyal digital pada suatu rangkaian. Alat ini sangat berguna dalam perbaikan, pengujian, dan analisis rangkaian digital, karena memberikan informasi instan mengenai keadaan logika dari sebuah titik pengujian.

1. Pencacah Shift Register (Shift Register Counters) Pencacah shift register merupakan kategori khusus dari rangkaian sekuensial digital yang dibentuk dari serangkaian flip-flop yang tersusun dalam konfigurasi shift register dasar. Karakteristik utama dari shift register adalah kemampuannya untuk menggeser data secara serial dari satu flip-flop ke flip-flop berikutnya dengan setiap pulsa clock. Namun, untuk mengubah shift register menjadi sebuah pencacah yang menghasilkan urutan keadaan yang spesifik, diperlukan penambahan jalur umpan balik dari output ke inputnya. Umpan balik ini secara efektif "memasukkan" nilai baru ke dalam input flip-flop pertama berdasarkan kondisi output flip-flop terakhir, sehingga menciptakan siklus keadaan yang berulang dan telah ditentukan sebelumnya. Proses ini membedakannya secara fundamental dari shift register murni yang hanya melakukan pergeseran data tanpa pola berulang yang spesifik.

2. Shift Counter (Johnson Counter) Shift counter, yang secara luas dikenal sebagai Johnson counter, adalah jenis shift register counter yang sangat khas, dibedakan oleh skema umpan balik terbalik (inverse feedback). Perbedaan mendasar ini, jika dibandingkan dengan ring counter yang menggunakan umpan balik langsung (output Q ke input D), terletak pada cara output flip-flop terakhir dihubungkan kembali ke input flip-flop pertama. Umpan balik terbalik ini memastikan bahwa logika yang masuk ke flip-flop pertama adalah kebalikan dari output flip-flop terakhir.

Susunan (Konstruksi):

Dengan J-K Flip-Flop: Seperti yang digambarkan pada Figure 11.47, jika sebuah shift counter dibangun menggunakan J-K flip-flop (misalnya IC 74LS76), output Q dari flip-flop terakhir (misalnya U2:B pada Figure 11.47) dihubungkan ke input K dari flip-flop pertama (U1:A), dan secara bersamaan, output (komplemen dari Q) dari flip-flop terakhir diumpan balikkan ke input J dari flip-flop pertama. Konfigurasi ini memastikan bahwa J dan K dari flip-flop pertama selalu menerima input yang berlawanan, memungkinkannya untuk toggle (berubah keadaan) berdasarkan output flip-flop terakhir.

Dengan D Flip-Flop: Jika shift register menggunakan D flip-flop untuk konstruksinya, output Q dari flip-flop terakhir diumpan balikkan ke input D dari flip-flop pertama. (Perlu dicatat bahwa dalam literatur umum Johnson counter dengan D-FF sering menggunakan dari FF terakhir ke D FF pertama untuk menghasilkan pola yang sama).

Dengan R-S Flip-Flop: Apabila flip-flop tipe R-S digunakan, output Q dari flip-flop terakhir dihubungkan ke input R dari flip-flop pertama, dan output dihubungkan ke input S dari flip-flop pertama.

Urutan Keadaan (Four-bit Shift Counter): Untuk sebuah four-bit shift counter (yang ditunjukkan pada Figure 11.47), urutan keadaannya sangat unik dan simetris. Jika pencacah diinisialisasi ke kondisi semua '0' (0000), pola pergeseran bit akan membentuk "string" '1' yang masuk dari satu sisi dan "string" '0' yang masuk dari sisi lainnya. Urutan keadaannya adalah sebagai berikut:

Keadaan Awal: 0000

Pulsa clock pertama: Output dari flip-flop terakhir (yang semula '1' karena Q adalah '0') diumpan balikkan ke input flip-flop pertama. Hasilnya, '1' masuk dari kiri, dan '0' lainnya bergeser ke kanan, sehingga keadaan menjadi 1000.

Pulsa clock kedua: '1' lain masuk dari kiri, menggeser '1' yang sudah ada ke kanan. Keadaan menjadi 1100.

Pulsa clock ketiga: '1' ketiga masuk dari kiri. Keadaan menjadi 1110.

Pulsa clock keempat: '1' keempat masuk dari kiri. Keadaan menjadi 1111.

Pulsa clock kelima: Output dari flip-flop terakhir kini adalah '0' (karena Q adalah '1'). '0' ini diumpan balikkan ke input flip-flop pertama. '1' di flip-flop pertama bergeser ke kanan. Keadaan menjadi 0111.

Pulsa clock keenam: '0' lain masuk dari kiri. Keadaan menjadi 0011.

Pulsa clock ketujuh: '0' lain masuk dari kiri. Keadaan menjadi 0001.

Pulsa clock kedelapan: '0' lain masuk dari kiri. Keadaan kembali menjadi 0000.

Siklus 8 keadaan ini akan berulang. Keunggulan Johnson counter adalah kemampuannya menghasilkan 2N keadaan unik untuk N flip-flop, yang dua kali lebih banyak daripada ring counter dengan jumlah flip-flop yang sama.

3. Aplikasi Shift Counter (Johnson Counter) Karena kemampuannya untuk menghasilkan urutan keadaan yang spesifik dan jumlah keadaan yang lebih banyak (2N), shift counter memiliki berbagai aplikasi praktis dalam sistem digital. Penggunaannya meliputi:

Generator Sekuensial: Untuk menghasilkan deretan pulsa atau sinyal kontrol yang kompleks dan berurutan.

Konverter Kode: Mengubah satu pola kode menjadi pola kode lain yang unik, seringkali dengan decoding yang lebih sederhana karena transisi satu bit pada satu waktu (untuk sebagian besar siklus).

Pembagi Frekuensi (Frequency Dividers): Dapat digunakan untuk membagi frekuensi clock input dengan faktor 2N, menciptakan sinyal clock dengan frekuensi yang lebih rendah untuk keperluan timing sistem.

Shift counter, atau yang juga disebut Johnson counter, adalah varian dari shift register counter yang dikenal karena metode umpan balik terbalik dari flip-flop output terakhir ke flip-flop input pertamanya. Teknik umpan balik ini, yang membedakannya dari ring counter, memungkinkan shift counter untuk menghasilkan serangkaian keadaan yang khas dan lebih panjang. Sebagai contoh, untuk sebuah pencacah N-bit, Johnson counter mampu menghasilkan 2N kondisi yang berbeda, yang setara dengan dua kali lipat jumlah kondisi yang dihasilkan oleh ring counter dengan jumlah flip-flop yang sama.

Mekanisme umpan balik terbalik ini menciptakan pola "string" bit logika '1' yang masuk dari satu sisi dan "string" bit logika '0' yang masuk dari sisi berlawanan secara bersamaan pada setiap pulsa clock. Hasilnya adalah pola hitungan yang sangat spesifik, misalnya, untuk pencacah 4-bit, polanya adalah 0000 1000 1100 1110 1111 0111 0011 0001 0000. Kemampuan shift counter untuk menghasilkan urutan yang unik dan panjang membuatnya menjadi pilihan yang cocok untuk berbagai aplikasi, seperti pembangun sekuens, konverter kode, dan pembagi frekuensi.

A. Langkah-langkah Percobaan

.png)

Komentar

Posting Komentar